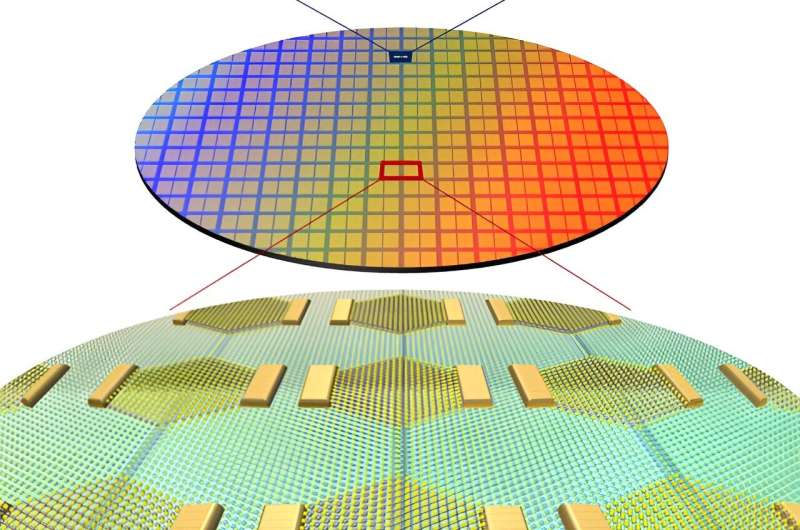

This figure illustrates the synthesis of 1D mirror-metal twin joints by van der Waals epitaxial growth (top) and the large-area 2D semiconductor integrated circuit constructed based on these joints (bottom). By controlling the crystal structure of molybdenum disulfide at the atomic level using van der Waals epitaxial growth, 1D mirror-metal twin joints were freely synthesized at desired locations on a large scale. These joints were applied as gate electrodes to implement ultraminiaturized 2D semiconductor transistors with atomic-scale channel lengths. Credit: Institute of Basic Science

A research team led by Jo Moon-Ho, director of the Center for Van der Waals Quantum Solids at the Institute for Basic Science (IBS), has implemented a new method to achieve epitaxial growth of 1D metallic materials with a width of less than 1 nm. The group applied this process to develop a new structure for 2D semiconductor logic circuits. In particular, they used the 1D metals as the gate electrode of the ultra-miniaturized transistor.

This search appears in Natural nanotechnology.

Integrated devices based on two-dimensional (2D) semiconductors, which exhibit excellent properties even at the ultimate limit of material thickness down to the atomic scale, are at the heart of fundamental and applied research worldwide. However, the realization of such ultra-miniaturized transistor devices capable of controlling the motion of electrons to within a few nanometers, not to mention the development of the manufacturing process for such integrated circuits, has faced considerable technical challenges.

The degree of integration of semiconductors is determined by the width and control efficiency of the gate electrode, which controls the flow of electrons in the transistor. In conventional semiconductor manufacturing processes, it is impossible to reduce the gate length below a few nanometers due to the limitations of lithography resolution.

To solve this technical problem, the research team exploited the fact that the mirror twin boundary (MTB) of molybdenum disulfide (MoS2), a 2D semiconductor, is a 1D metal with a width of only 0.4 nm. They used it as a gate electrode to overcome the limitations of the lithography process.

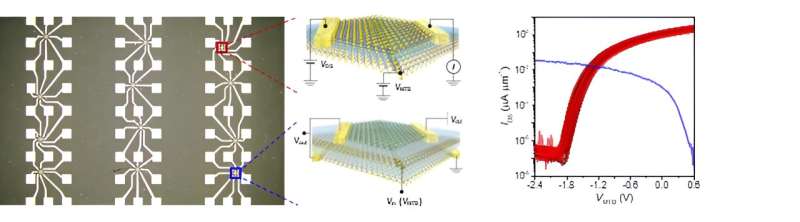

This figure shows an optical microscope image of the integrated circuit based on 1D twin-mirror boundary gates (left), a schematic of the ultra-miniaturized transistor and inverter devices that make up the circuit (center), and the performance evaluation of these devices (right). The 1D twin-mirror boundary process developed by the research team was not limited to the miniaturization of individual devices, but was successfully used to build large-area, highly integrated electronic circuits. Credit: Institute for Basic Science

In this study, the 1D MTB metallic phase was obtained by controlling the crystal structure of the existing 2D semiconductor at the atomic level, thereby transforming it into 1D MTB. This represents a significant advance not only for next-generation semiconductor technology but also for basic materials science, as it demonstrates the large-scale synthesis of new material phases through artificial control of crystal structures.

The IEEE International Roadmap for Devices and Systems (IRDS) predicts that semiconductor node technology will reach about 0.5 nm by 2037, with transistor gate lengths of 12 nm. The research team demonstrated that the channel width modulated by the applied electric field from the 1D MTB gate can be as small as 3.9 nm, significantly exceeding the futuristic prediction.

The 1D MTB transistor developed by the research team also offers advantages in circuit performance. Technologies such as FinFET or Gate-All-Around, adopted for the miniaturization of silicon semiconductor devices, suffer from parasitic capacitance due to their complex device structures, which leads to instability in highly integrated circuits. In contrast, the 1D MTB transistor can minimize parasitic capacitance due to its simple structure and extremely narrow gate width.

Director Jo Moon-Ho commented, “The 1D metal phase obtained by epitaxial growth is a new material process that can be applied to ultra-miniaturized semiconductor processes. It is expected to become a key technology for the development of various low-power and high-performance electronic devices in the future.”

More information:

Integrated 1D epitaxial mirror twin boundaries for ultra-sized 2D MoS2 field effect transistors, Natural nanotechnology (2024). DOI: 10.1038/s41565-024-01706-1

Provided by the Institute of Basic Sciences

Quote:Scientists Discover Way to ‘Grow’ Sub-Nanometer-Sized Transistors (July 3, 2024) Retrieved July 3, 2024 from https://phys.org/news/2024-07-scientists-nanometer-sized-transistors.html

This document is subject to copyright. Apart from any fair dealing for the purpose of private study or research, no part may be reproduced without written permission. The content is provided for informational purposes only.